# Scalable abstractions for general-purpose parallel computation

James W. Hanlon

A thesis submitted to the University of Bristol in accordance with the requirements of the degree Doctor of Philosophy in the Faculty of Engineering, Department of Computer Science, March 2014.

70,000 words.

Copyright © 2014 James W. Hanlon, some rights reserved.

This work is licensed under the Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License.

http://creativecommons.org/licenses/by-nc-nd/4.0/

#### Abstract

Parallelism has become the principal means of sustaining growth in computational performance but there has been relatively little development in *general-purpose* computer architectures or programming models that can deal effectively with large amounts of it. A new general-purpose model of parallel computing would enable standardisation between architectures, high-volume production and software that is portable between different machines, now and as they develop with future technology. There is substantial opportunity to support this in emerging areas of embedded computing, where the problems of sensing, interaction and decision making can exploit large amounts of parallelism.

This thesis demonstrates the essential aspects of a *scalable* general-purpose model of parallel computation by proposing a *Universal Parallel Architecture* (UPA), based on a highly-connected communication network, and a high-level parallel programming language for it called *sire* that can be compiled using simple techniques. The design of sire combines the essential capabilities of shared-memory programming with the benefits of message passing to support a range of programming paradigms and to provide powerful capabilities for *abstraction* to build and compose subroutines and data structures in a distributed context. The design also enables program code to be distributed at run time to reuse memory and for processor allocation to be dealt with during compilation so that the overheads of using distributed parallelism are minimal.

To evaluate whether the UPA is *practical* to build, a high-level implementation model using current technologies is described. It demonstrates that the cost of generality is relatively small; for a system with 4,096 processors, an overall investment of around 25% of the system is required for the communication network. Executing on specific UPA implementations, sire's primitives for parallelism, communication and abstraction incur minimal overheads, demonstrating its close correspondence to the UPA and its scalability. Furthermore, as well as executing highly-parallel programs, the UPA can support sequential programming techniques by emulating large memories, allowing general sequential programs to be executed with a factor of 2 to 3 overhead when compared to contemporary sequential machines.

#### Acknowledgements

My PhD has been a fantastic experience in which I have had free reign to pursue a line of research that has been fascinating, even though at times, hard to define. I owe a great deal of thanks to my supervisor Simon Hollis who originally encouraged me to embark on it and who has been so supportive throughout, and to David May who has provided endless inspiration and guidance.

There have been a number of people who have contributed to this work in various ways, to whom I am also very grateful: Henk Muller and Simon McIntosh-Smith who have provided valuable advice and discussion throughout; Simon Knowles, Paul Winsor and Ian Stewart who have provided their expertise and helped me to put my work in context; Paul Kelly who was kind enough to host me for a year in his research group at Imperial College in London; and Richard Osborne for his help getting to grips with the XS1 architecture and for the fast emulator he developed.

Of course, success with my PhD has not only required academic and technical guidance, but also moral support and distractions from the intensity of working alone; thank you to my colleagues and friends, particularly Chris Jackson, Markus Jalsenius, Leon Atkins, Steve Kerrison and James Pallister for this.

Finally, I would like to thank the EPSRC for providing the financial support for my studies.

## Author's declaration

I declare that the work in this dissertation was carried out in accordance with the requirements of the University's Regulations and Code of Practice for Research Degree Programmes and that it has not been submitted for any other academic award. Except where indicated by specific reference in the text, the work is the candidate's own work. Work done in collaboration with, or with the assistance of, others, is indicated as such. Any views expressed in the dissertation are those of the author.

Signed:

Date:

# CONTENTS

| List of Figures xiii |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                            |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|

| Lis                  | st of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | xv                                                                                                         |  |  |

| Lis                  | st of Processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | xvii                                                                                                       |  |  |

| 1                    | Introduction1.1Parallelism in computer architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |  |  |

| ı.                   | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9                                                                                                          |  |  |

| 2<br>3<br>4          | Parallel computation         2.1       Parallelism and communication         2.2       Models         2.3       Summary         2.3       Summary         3.1       Principles         3.2       Criteria for a general-purpose parallel-programming language         3.3       Survey of programming and compilation approaches         3.4       Summary         4.1       Universal communication networks         4.2       Switching mechanics         4.3       Processing         4.4       A short survey of real machine architectures         4.5       Summary | <ol> <li>17</li> <li>14</li> <li>28</li> <li>38</li> <li>41</li> <li>41</li> <li>54</li> <li>58</li> </ol> |  |  |

| П                    | The UPA and the sire language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 65                                                                                                         |  |  |

| 5                    | The Universal Parallel Architecture5.1Overview.5.2Interconnect.5.3Processing.5.4Memory.5.5Packaging.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                            |  |  |

| 6                    | The sire programming language         6.1       The model of computation         6.2       Notation         6.3       Overview                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>71</b><br>71<br>71<br>72                                                                                |  |  |

|                | 6.4                                                                                                                                            | Primitive commands                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73                                                                                                                                             |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|                | 6.5                                                                                                                                            | Structured commands                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 75                                                                                                                                             |

|                | 6.6                                                                                                                                            | Types, names and scope                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 77                                                                                                                                             |

|                | 6.7                                                                                                                                            | Composition                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 80                                                                                                                                             |

|                | 6.8                                                                                                                                            | Servers                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 83                                                                                                                                             |

|                | 6.9                                                                                                                                            | Replication                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 87                                                                                                                                             |

|                | 6.10                                                                                                                                           | Expressions and elements                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 90                                                                                                                                             |

|                | 6.11                                                                                                                                           | Procedural abstraction                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 91                                                                                                                                             |

|                | 6.12                                                                                                                                           | Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 97                                                                                                                                             |

|                | 6.13                                                                                                                                           | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98                                                                                                                                             |

| 7              | Sire                                                                                                                                           | programming structures 10                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 01                                                                                                                                             |

|                | 7.1                                                                                                                                            | Process structures                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 01                                                                                                                                             |

|                | 7.2                                                                                                                                            | Server structures                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16                                                                                                                                             |

|                | 7.3                                                                                                                                            | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28                                                                                                                                             |

| 8              | Com                                                                                                                                            | bilation of sire to the UPA 1:                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31                                                                                                                                             |

|                | 8.1                                                                                                                                            | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31                                                                                                                                             |

|                | 8.2                                                                                                                                            | Program transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                |

|                | 8.3                                                                                                                                            | Machine target                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                |

|                | 8.4                                                                                                                                            | Run-time kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                |

|                | 8.5                                                                                                                                            | Code generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                |

|                | 8.6                                                                                                                                            | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                |

| ш              | Eva                                                                                                                                            | luation of implementation cost and performance 1                                                                                                                                                                                                                                                                                                                                                                                                                                | 79                                                                                                                                             |

|                |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                |

| 9              |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 81                                                                                                                                             |

| 9              | 9.1                                                                                                                                            | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 81                                                                                                                                             |

| 9              | 9.1<br>9.2                                                                                                                                     | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 81<br>81                                                                                                                                       |

| 9              | 9.1                                                                                                                                            | Overview       1         Background       1         Implementation model       1                                                                                                                                                                                                                                                                                                                                                                                                | 81<br>81<br>84                                                                                                                                 |

| 9              | 9.1<br>9.2<br>9.3<br>9.4                                                                                                                       | Overview       1         Background       1         Implementation model       1         Model parameters       1                                                                                                                                                                                                                                                                                                                                                               | 81<br>81<br>84<br>86                                                                                                                           |

| 9              | 9.1<br>9.2<br>9.3<br>9.4<br>9.5                                                                                                                | Overview       1         Background       1         Implementation model       1         Model parameters       1         Cost and scaling       1                                                                                                                                                                                                                                                                                                                              | 81<br>81<br>84<br>86<br>91                                                                                                                     |

| 9              | 9.1<br>9.2<br>9.3<br>9.4                                                                                                                       | Overview       1         Background       1         Implementation model       1         Model parameters       1                                                                                                                                                                                                                                                                                                                                                               | 81<br>81<br>84<br>86<br>91                                                                                                                     |

| _              | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6                                                                                                         | Overview       1         Background       1         Implementation model       1         Model parameters       1         Cost and scaling       1         Discussion       2                                                                                                                                                                                                                                                                                                   | 81<br>81<br>84<br>86<br>91                                                                                                                     |

| _              | <ul> <li>9.1</li> <li>9.2</li> <li>9.3</li> <li>9.4</li> <li>9.5</li> <li>9.6</li> </ul> Perfc                                                 | Overview       1         Background       1         Implementation model       1         Model parameters       1         Cost and scaling       1         Discussion       2         rmance evaluation of the UPA and sire       20                                                                                                                                                                                                                                            | 81<br>84<br>86<br>91<br>00                                                                                                                     |

| _              | <ul> <li>9.1</li> <li>9.2</li> <li>9.3</li> <li>9.4</li> <li>9.5</li> <li>9.6</li> </ul> Perfc <ul> <li>10.1</li> </ul>                        | Overview       1         Background       1         Implementation model       1         Implementation model       1         Model parameters       1         Cost and scaling       1         Discussion       2         rmance evaluation of the UPA and sire       20         Simulation model       2                                                                                                                                                                      | 81<br>81<br>84<br>86<br>91<br>00<br><b>05</b>                                                                                                  |

| _              | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br><b>Perfc</b><br>10.1<br>10.2<br>10.3                                                                 | Overview       1         Background       1         Implementation model       1         Model parameters       1         Cost and scaling       1         Discussion       2         rmance evaluation of the UPA and sire       2         Simulation model       2         Efficiency of sire primitives       2         Emulation of large sequential memories       2                                                                                                       | <ul> <li>81</li> <li>84</li> <li>86</li> <li>91</li> <li>00</li> <li>05</li> <li>08</li> <li>17</li> </ul>                                     |

| _              | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br><b>Perfc</b><br>10.1<br>10.2<br>10.3                                                                 | Overview       1         Background       1         Implementation model       1         Model parameters       1         Cost and scaling       1         Discussion       2         rmance evaluation of the UPA and sire       2         Simulation model       2         Efficiency of sire primitives       2                                                                                                                                                              | <ul> <li>81</li> <li>84</li> <li>86</li> <li>91</li> <li>00</li> <li>05</li> <li>08</li> <li>17</li> </ul>                                     |

| 10             | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br><b>Perfc</b><br>10.1<br>10.2<br>10.3<br>10.4<br><b>Sum</b>                                           | Overview       1         Background       1         Implementation model       1         Implementation model       1         Model parameters       1         Cost and scaling       1         Discussion       2         rmance evaluation of the UPA and sire       20         Simulation model       2         Efficiency of sire primitives       2         Emulation of large sequential memories       2         Discussion       2         mary and conclusions       2 | <ul> <li>81</li> <li>84</li> <li>86</li> <li>91</li> <li>00</li> <li>05</li> <li>08</li> <li>17</li> <li>24</li> <li>29</li> </ul>             |

| 10             | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br><b>Perfc</b><br>10.1<br>10.2<br>10.3<br>10.4<br><b>Sum</b><br>11.1                                   | Overview1Background1Implementation model1Model parameters1Cost and scaling1Discussion2rmance evaluation of the UPA and sire2Simulation model2Efficiency of sire primitives2Emulation of large sequential memories2Discussion2nary and conclusions2Background2                                                                                                                                                                                                                   | <ul> <li>81</li> <li>84</li> <li>86</li> <li>91</li> <li>00</li> <li>05</li> <li>08</li> <li>17</li> <li>24</li> <li>29</li> <li>29</li> </ul> |

| 10             | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br><b>Perfc</b><br>10.1<br>10.2<br>10.3<br>10.4<br><b>Sum</b><br>11.1<br>11.2                           | Overview1Background1Implementation model1Model parameters1Cost and scaling1Discussion2rmance evaluation of the UPA and sire2Simulation model2Efficiency of sire primitives2Emulation of large sequential memories2Discussion2nary and conclusions2Background2Contributions2                                                                                                                                                                                                     | 81<br>84<br>86<br>91<br>00<br>05<br>08<br>17<br>24<br>29<br>29<br>30                                                                           |

| 10             | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br><b>Perfc</b><br>10.1<br>10.2<br>10.3<br>10.4<br><b>Sum</b><br>11.1<br>11.2                           | Overview1Background1Implementation model1Model parameters1Cost and scaling1Discussion2rmance evaluation of the UPA and sire2Simulation model2Efficiency of sire primitives2Emulation of large sequential memories2Discussion2nary and conclusions2Background2                                                                                                                                                                                                                   | 81<br>84<br>86<br>91<br>00<br>05<br>08<br>17<br>24<br>29<br>29<br>30                                                                           |

| 10             | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br><b>Perfc</b><br>10.1<br>10.2<br>10.3<br>10.4<br><b>Sum</b><br>11.1<br>11.2                           | Overview1Background1Implementation model1Model parameters1Cost and scaling1Discussion2rmance evaluation of the UPA and sire20Simulation model2Efficiency of sire primitives2Emulation of large sequential memories2Discussion2nary and conclusions2Background2Contributions2Conclusions and future work2                                                                                                                                                                        | 81<br>84<br>86<br>91<br>00<br>05<br>08<br>17<br>24<br>29<br>29<br>30                                                                           |

| 10             | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br><b>Perfc</b><br>10.1<br>10.2<br>10.3<br>10.4<br><b>Sum</b><br>11.1<br>11.2<br>11.3<br><b>ference</b> | Overview1Background1Implementation model1Model parameters1Cost and scaling1Discussion2rmance evaluation of the UPA and sire2Simulation model2Efficiency of sire primitives2Emulation of large sequential memories2Discussion2nary and conclusions2Background2Contributions2Conclusions and future work2es2                                                                                                                                                                      | 81<br>84<br>86<br>91<br>00<br>05<br>08<br>17<br>24<br>29<br>29<br>30<br>32                                                                     |

| 10<br>11<br>Re | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br><b>Perfc</b><br>10.1<br>10.2<br>10.3<br>10.4<br><b>Sum</b><br>11.1<br>11.2<br>11.3<br><b>ference</b> | Overview1Background1Implementation model1Model parameters1Cost and scaling1Discussion2rmance evaluation of the UPA and sire2Simulation model2Efficiency of sire primitives2Emulation of large sequential memories2Discussion2nary and conclusions2Background2Contributions2Conclusions and future work2es2                                                                                                                                                                      | 81<br>84<br>86<br>91<br>00<br>05<br>08<br>17<br>24<br>29<br>30<br>32<br>33<br>33<br>53                                                         |

| 10<br>11<br>Re | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br><b>Perfc</b><br>10.1<br>10.2<br>10.3<br>10.4<br><b>Sum</b><br>11.1<br>11.2<br>11.3<br><b>ference</b> | Overview1Background1Implementation model1Model parameters1Cost and scaling1Discussion2rmance evaluation of the UPA and sire20Simulation model2Efficiency of sire primitives2Emulation of large sequential memories2Discussion2nary and conclusions2Background2Contributions2conclusions and future work2es2syntax2                                                                                                                                                              | 81<br>84<br>86<br>91<br>00<br>05<br>08<br>17<br>24<br>29<br>29<br>30<br>32<br>33<br>33<br>53                                                   |

| A.4   | Representation of values            |

|-------|-------------------------------------|

| A.5   | Character set                       |

| A.6   | Comments                            |

| A.7   | Keywords                            |

| B Ano | verview of the XS1 architecture 265 |

| B.1   | Overview                            |

| B.2   | Memory access                       |

| B.3   | Branching and procedure calls       |

| B.4   | Resources                           |

| B.5   | Communication                       |

| B.6   | Events and interrupts               |

| B.7   | Threading                           |

| B.8   | Locks                               |

# LIST OF FIGURES

| 1.1  | Components of a general-purpose form of computation and the abstractions involved. | 3 |

|------|------------------------------------------------------------------------------------|---|

| 2.1  | Communication in message passing and shared memory                                 | 2 |

| 3.1  | Decompositions of a 3D domain                                                      | 8 |

| 3.2  | Recursive decompositions                                                           | 9 |

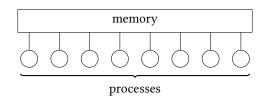

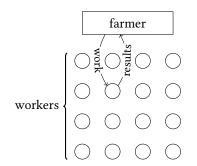

| 3.3  | The shared memory paradigm                                                         | 2 |

| 3.4  | Regular process structures                                                         | 3 |

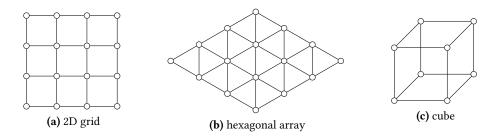

| 3.5  | Regular data-flow structures                                                       | 3 |

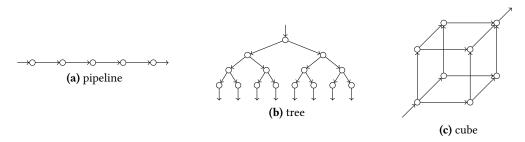

| 3.6  | The task farm paradigm                                                             | 4 |

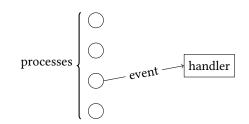

| 3.7  | The event handler paradigm                                                         | 4 |

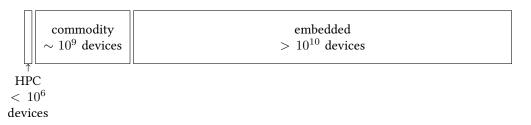

| 3.8  | The spectrum of computing                                                          | 8 |

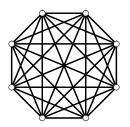

| 4.1  | A complete network                                                                 | 2 |

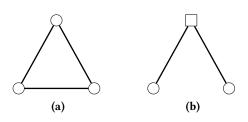

| 4.2  | Illustrations of the network model                                                 | 2 |

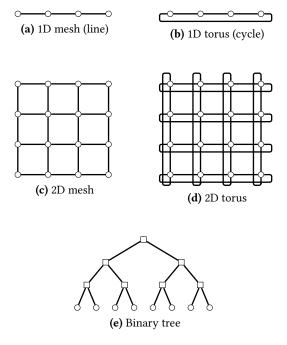

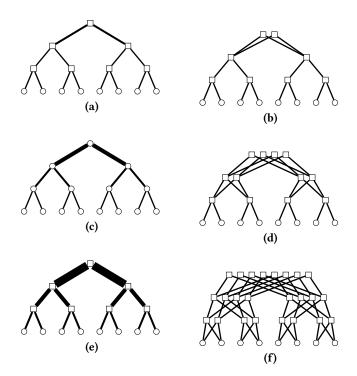

| 4.3  | Examples of common bounded-degree networks                                         | 5 |

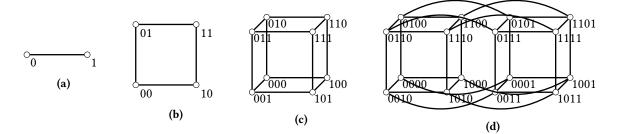

| 4.4  | Hypercube networks                                                                 | 6 |

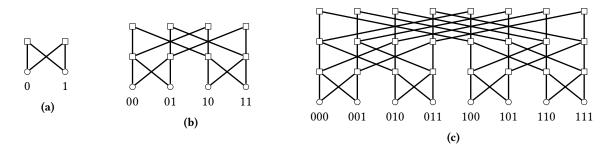

| 4.5  | Butterfly networks                                                                 | 6 |

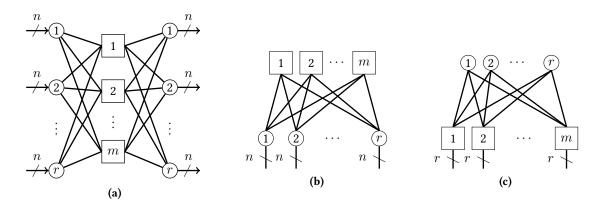

| 4.6  | Clos networks                                                                      | 6 |

| 4.7  | Fat tree networks                                                                  | 7 |

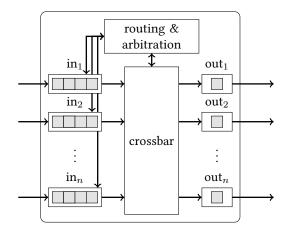

| 4.8  | Block architecture of an input-buffered crossbar switch                            | 4 |

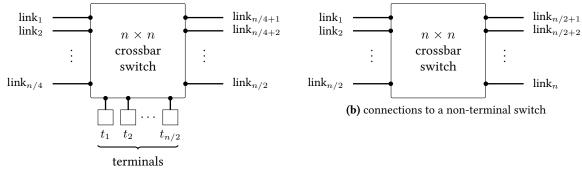

| 4.9  |                                                                                    | 4 |

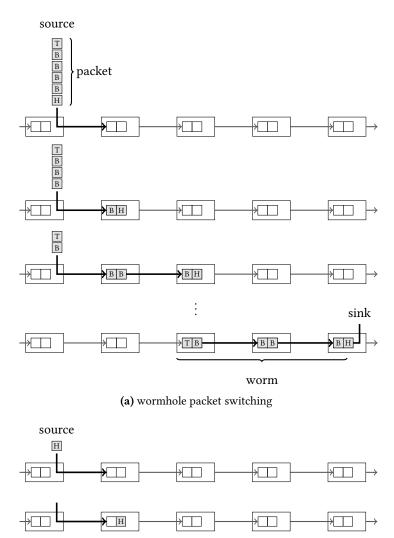

| 4.10 | 1 0                                                                                | 6 |

| 4.11 | Communication startup latency                                                      | 9 |

| 5.1  | A high-level view of the UPA                                                       | 7 |

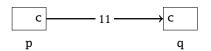

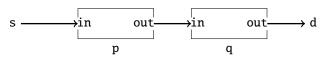

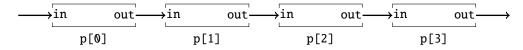

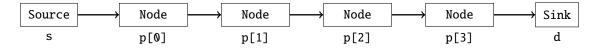

| 7.1  | A pipeline process structure                                                       | 2 |

| 7.2  | A $2 \times 2$ grid process structure                                              | 5 |

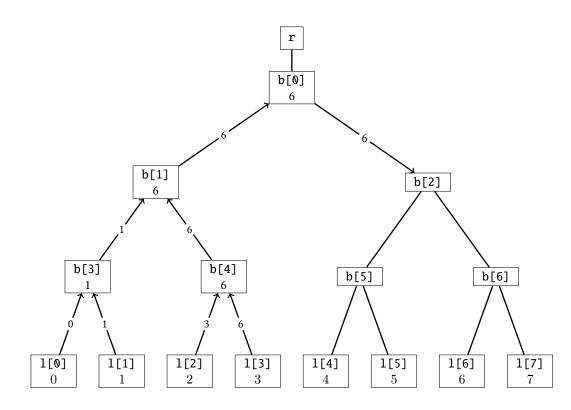

| 7.3  | A depth-3 binary tree process structure                                            | 0 |

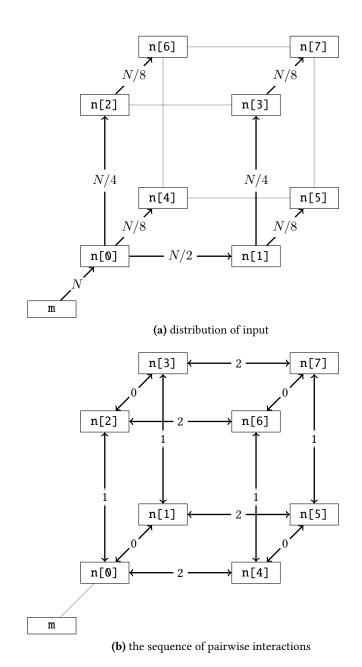

| 7.4  | A 3D hypercube process structure                                                   | 3 |

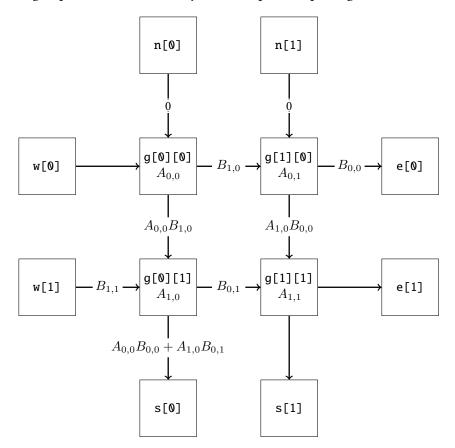

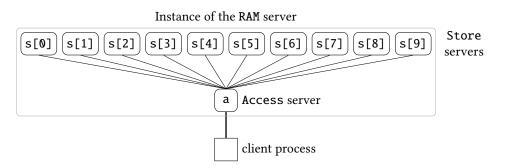

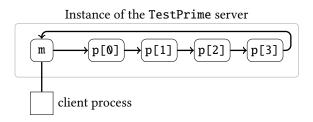

| 7.5  | A server that provides a random access memory                                      |   |

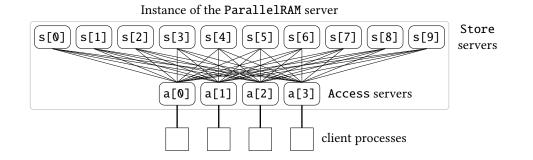

| 7.6  | A server that provides a parallel random access memory                             |   |

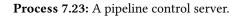

| 7.7  | An embedded pipeline process structure                                             | 7 |

| 8.1  | An illustration of deadlock arising from many-to-one communications                |   |

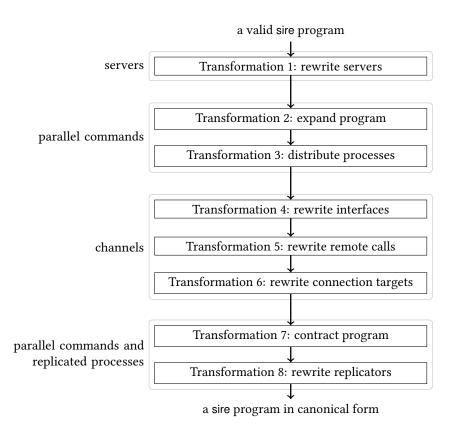

| 8.2  | The sequence of transformations to produce the canonical form                      | 5 |

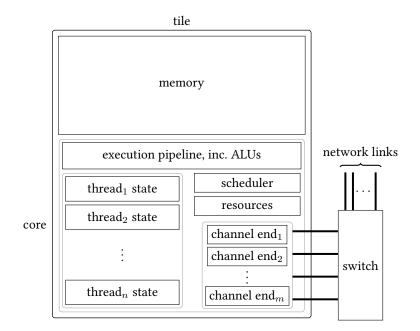

| 8.3  | A block diagram of the XS1 architecture                                            | 1 |

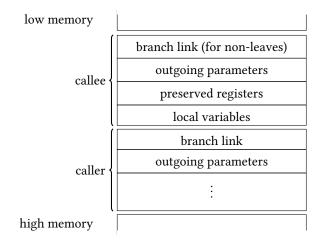

| 8.4  | Example stack frame layout illustrating the calling convention                     | 3 |

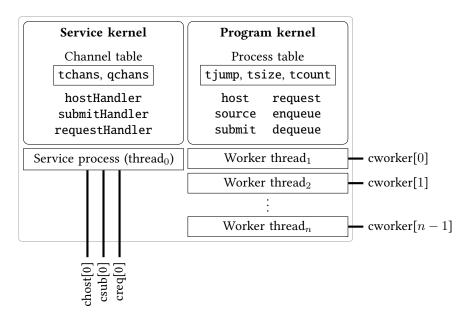

| 8.5  | Block diagram of the per-processor run-time kernel                                 | 5 |

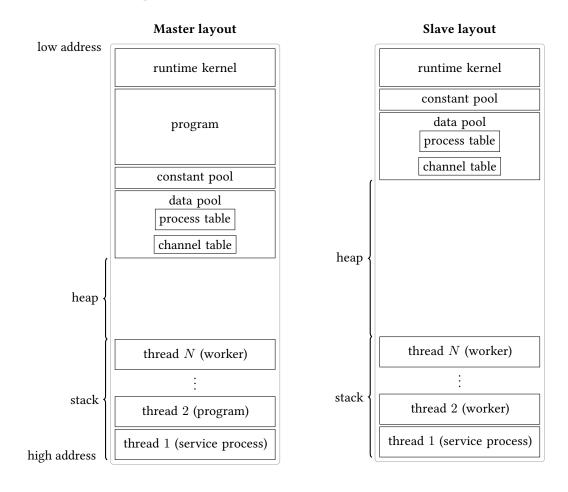

| 8.6  | Master and slave memory layouts produced by compilation                            | 5 |

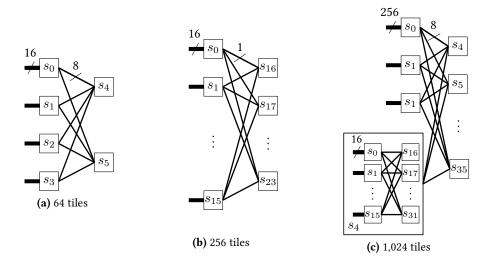

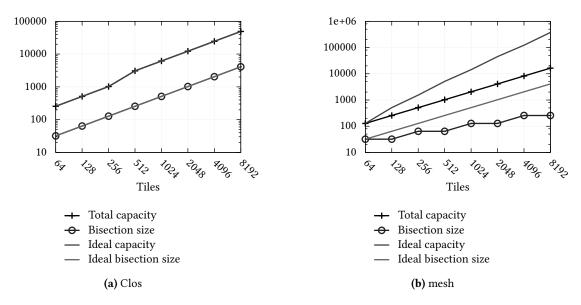

| 9.1  | Example Clos switch topologies                                                     | 3 |

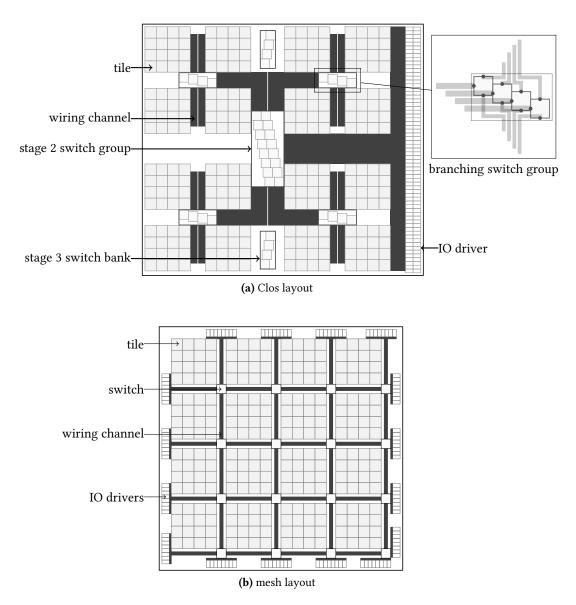

| 9.2  | Layouts for 256-tile Clos and mesh networks for the UPA processing chip 18         |   |

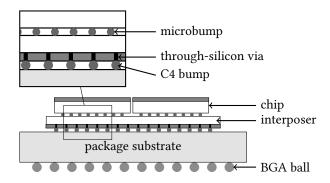

| 9.3  | Cut through view of the packaging                                                  | 8 |

| 9.4  | Chip layouts on the interposer                                                     | 8 |

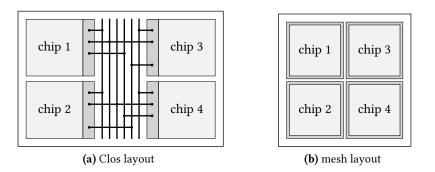

| 9.5   | Scaling of switch requirement and diameter                              |  |  |

|-------|-------------------------------------------------------------------------|--|--|

| 9.6   | Scaling of capacity and bisection size                                  |  |  |

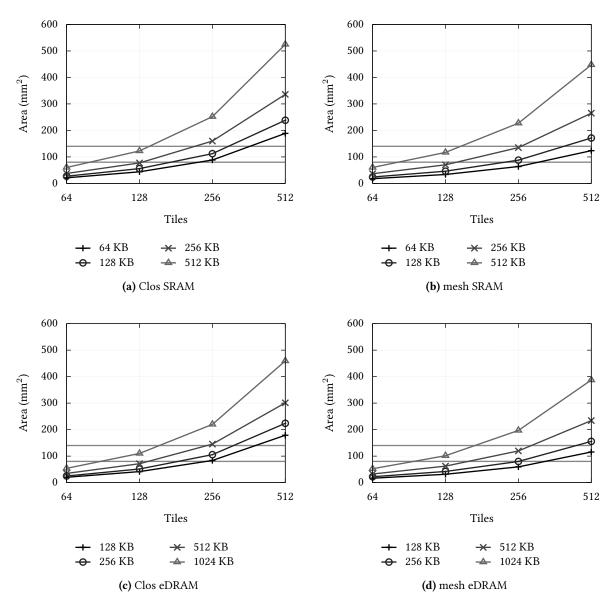

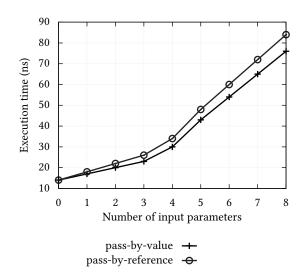

| 9.7   | Total chip area.         194                                            |  |  |

| 9.8   | Chip area components                                                    |  |  |

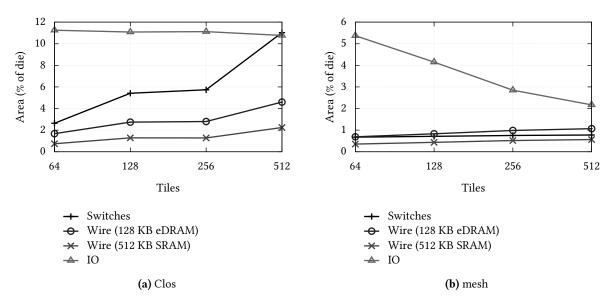

| 9.9   | Scaling of the total interposer area                                    |  |  |

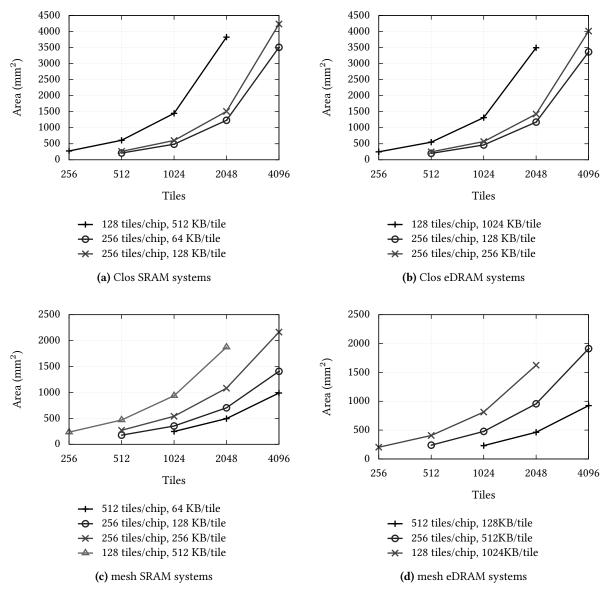

|       | Execution time for the local procedure-call benchmark                   |  |  |

| 10.2  | Execution time of server calls                                          |  |  |

| 10.3  | Execution time of remote calls                                          |  |  |

| 10.4  | Performance of process distribution                                     |  |  |

| 10.5  | Performance of the hypercube and tree process structures in sire        |  |  |

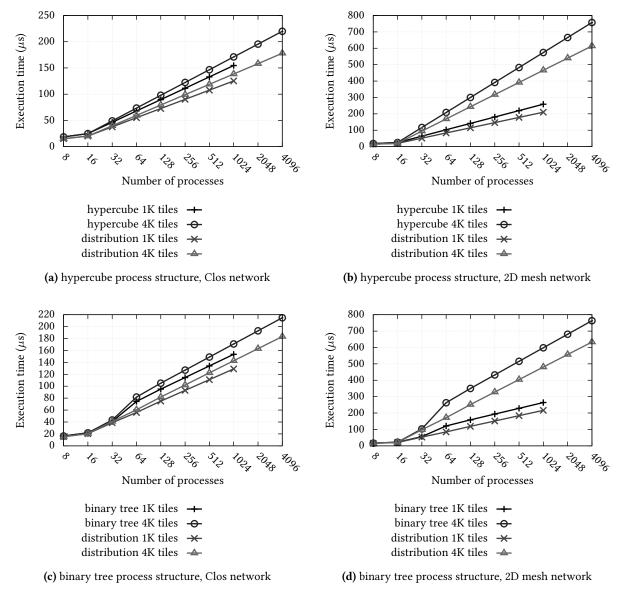

| 10.6  | Performance of the hypercube and binary tree process structures in sire |  |  |

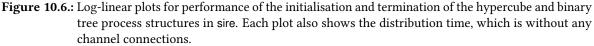

| 10.7  | Instruction mix of the Dhrystone and compiler benchmarks                |  |  |

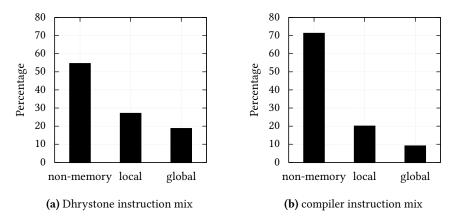

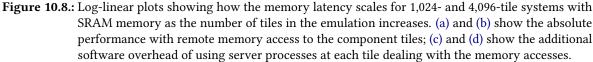

| 10.8  | Latency of memory emulations                                            |  |  |

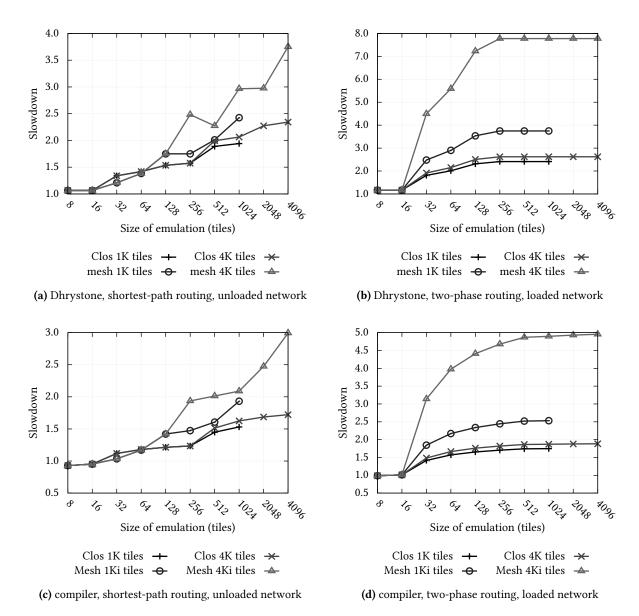

| 10.9  | Performance of the synthetic Dhrystone and compiler benchmarks          |  |  |

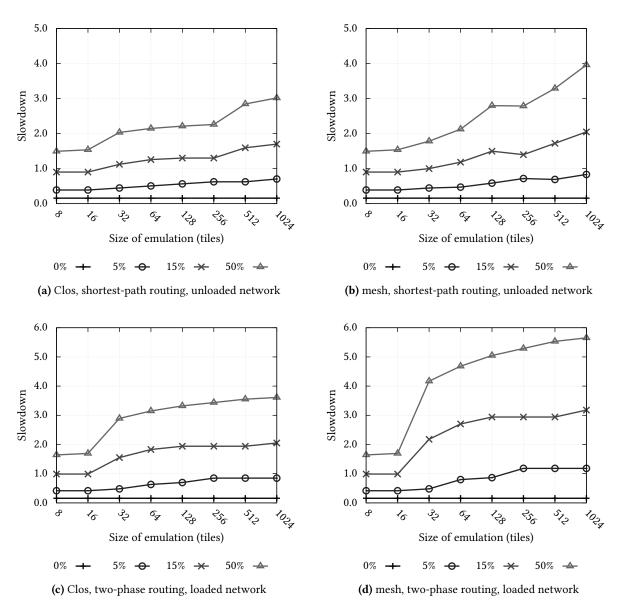

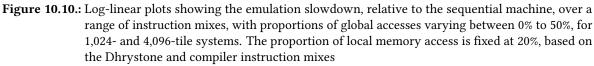

| 10.10 | 10.10 Slowdown of emulation over a range of instruction mixes           |  |  |

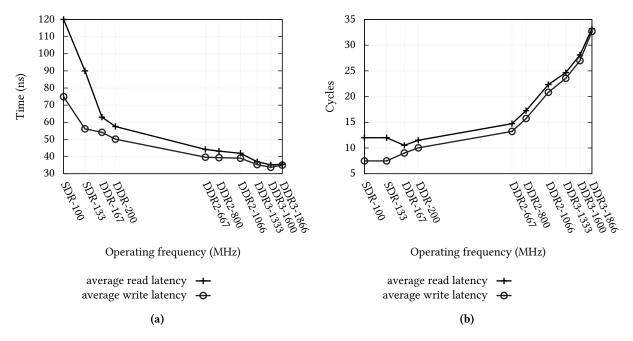

| 10.11 | 10.11 Average read and write latency for monolithic DRAM systems        |  |  |

# LIST OF TABLES

| 3.1  | A summary of the different parallel-programming paradigms                     |

|------|-------------------------------------------------------------------------------|

| 3.2  | Summary of parallel-programming languages and libraries                       |

| 4.1  | Summary of different sparse networks and their properties                     |

| 4.2  | A short survey of real parallel machine architectures                         |

| 8.1  | Values associated with each process in Process 8.3 after transformation 3     |

| 8.2  | Behaviour of Process 8.8                                                      |

| 8.3  | Overview of the kernel routines                                               |

| 8.4  | Constant values used in the run-time kernel                                   |

| 8.5  | Summary of the storage requirements per processor for the run-time kernel 156 |

| 8.6  | Local storage allocated by a worker thread to host an incoming process        |

| 9.1  | Parameters for the processing chip model                                      |

| 9.2  | Parameters for the interposer                                                 |

| 9.3  | ITRS data for global wires                                                    |

| 9.4  | Comparison of contemporary memory technologies                                |

| 9.5  | Selected memory capacities of SRAM and eDRAM 190                              |

| 9.6  | Cost-performance chips                                                        |

| 9.7  | Global wire lengths and their delays for selected Clos chips                  |

| 9.8  | Global wire lengths and their delays for selected mesh chips                  |

| 9.9  | Potential multi-chip Clos system configurations                               |

| 9.10 | Potential multi-chip mesh system configurations                               |

| 9.11 | A comparison of area and sequential capability of different processors        |

| 10.1 | Parameters for the network performance model                                  |

# LIST OF PROCESSES

| 7.1  | The replicated pipeline node                                      |

|------|-------------------------------------------------------------------|

| 7.2  | The pipeline source node                                          |

| 7.3  | The pipeline sink node                                            |

| 7.4  | The replicated grid node                                          |

| 7.5  | The replicated border nodes to source and sink from the grid      |

| 7.6  | The tree root node                                                |

| 7.7  | The replicated tree branch node                                   |

| 7.8  | The tree leaf node                                                |

| 7.9  | Hypercube distribution procedures                                 |

| 7.10 | A hypercube sorting procedure                                     |

| 7.11 |                                                                   |

| 7.12 | The replicated hypercube node                                     |

| 7.13 | A server that provides access to an array                         |

| 7.14 | A server that allows the internal array to be modified locally    |

| 7.15 | A stack server                                                    |

|      | A buffer server                                                   |

|      | A task farm farmer server                                         |

| 7.18 | A task farm worker process                                        |

| 7.19 | A server providing a distributed random access memory             |

| 7.20 | An access server that performs caching                            |

| 7.21 |                                                                   |

| 7.22 |                                                                   |

| 7.23 | A pipeline control server                                         |

| 8.1  | Compilation transformations example: input program                |

| 8.2  | Transformation example: stage 1                                   |

| 8.3  | Transformation example: stage 3                                   |

| 8.4  | Transformation example: stage 4                                   |

| 8.5  | Transformation example: stage 5                                   |

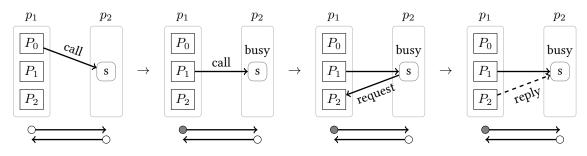

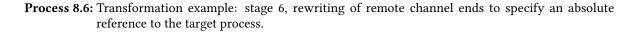

| 8.6  | Transformation example: stage 6                                   |

| 8.8  | A process that employs parallel recursion to distribute execution |

| 8.7  | Transformation example: stage 7                                   |

| 8.9  | A generalised version of Process 8.8                              |

| 8.10 | 0                                                                 |

| 8.11 |                                                                   |

# CHAPTER 1.

# INTRODUCTION

The rate of development of computing in the last century is unmatched by any other technology; consequently, it has become an integral part of science, commerce, industry and everyday life. Its success can be attributed two key factors: the proliferation of a single basic model of computation and the development of sympathetic implementation technologies that have supported an exponential growth in performance.

The conventional basic model of computation has been the *von Neumann architecture* [von45], which can be seen as an efficient realisation of Alan Turing's work on *universal computing machines* [Tur37]. In Turing's work, a computing machine is universal in the sense that, as well as being able to execute any program that it may be supplied as an input, it can emulate any other machine by reading both the description of the machine to be emulated, as well as the input. Making this universality efficient means that the cost of the machine and the performance of an emulation are both proportional to that of a hypothetical specialised device that implements directly the machine being emulated. This has allowed von Neumann machines to take over from special-purpose devices in many application areas as a cheaper and more flexible alternative.

The von Neumann model is based on the abstraction of a single large *randomly-accessible memory* in which both the program and data are stored and accessed by a *processor* that performs computational operations. Arbitrarily large programs and data sets can be handled by scaling the size of the memory and performance can be scaled by increasing the rate at which operations are performed. *Complementary metal-oxide-semiconductor* (CMOS) technology has provided a synergistic implementation technique for the model. It is a technology for densely integrating electronic circuits onto semiconductor materials and ways of scaling it have provided exponential increases in the density and operating frequency of devices.<sup>1</sup> This has provided according increases in memory capacity and processing rate and, driven by huge demand in consumer markets, this has led to rapid iterations of hardware, providing immediate benefits to existing software.

Inevitably, the scaling of frequency in CMOS devices has not continued indefinitely due to fundamental limits in its power efficiency, and since this was the principal way by which the performance of von Neumann machines was scaled, their performance has stopped scaling in the same way. This occurred around 2005 and since then, there have only been very modest increases in sequential performance. However, although operating frequency has stalled, the density of CMOS devices has continued to scale and is predicted to do so for the next 15 to 20 years [Int12a].

#### 1.1. Parallelism in computer architecture

It is now widely accepted that parallelism is the only known means of sustaining growth in computational performance [FM11, p. 109] and as the density of CMOS devices continues to scale, the microprocessor industry will produce designs with larger number of processors. Based on this, it looks increasingly certain that future systems will involve large numbers of processors,<sup>2</sup> potentially with thousands of cores per chip [Bor07]. There are many application areas that will be able to make

<sup>&</sup>lt;sup>1</sup>This scaling was first observed by Gordon Moore at Intel in 1965 and has since been known as *Moore's law* [Moo65]. It has since become a significant driver for the industry as a self-fulfilling prophecy.

<sup>&</sup>lt;sup>2</sup>This is reflected in the model used by the *International Technology Roadmap for Semiconductors* (ITRS) which was significantly revised in 2007, setting a basis of 4 processor cores per chip and projected a factor of 1.4x increase every technology generation, which is on average 2.5 years [Int12c, p. 14].

use of large amounts of parallelism. These include artificial intelligence, vision, graphics, natural language processing and human interaction. With continued scaling, these will increasingly be applied in *embedded systems* such as *robotics*, where there is enormous potential for the further application of computers.

The prevailing reaction from microprocessor designers since 2005 has been an evolutionary one to extend the von Neumann architecture with multiple processors that all access the same memory. These devices are known as *symmetric multiprocessors* (SMPs). They maintain compatibility with legacy code, which has perhaps come to be the most important driver in microprocessor design, but they exacerbate the problem of memory latency by increasing the competition for access bandwidth. This is known as the *von Neumann bottleneck* [Bac78]. The consequence is that this approach will likely face diminishing returns [ABC<sup>+</sup>06] and it is expected that SMPs will not scale well beyond around 24 cores [RKB<sup>+</sup>09]. They cannot therefore in the long term support large numbers of processors to provide the expected sustained growth in performance from parallelism.

Despite a preoccupation with the von Neumann model and frequency scaling in mainstream consumer devices, parallelism has been an active area of academic study and a practical means of scaling performance in *high-performance computing* (HPC) systems, which deliver performance far beyond that of a single processor. Typical state-of-the-art HPC systems employ hundreds of thousands of processors and have become essential in areas such as science and engineering for dealing with large-scale problems. Parallelism also has a long history in specialised devices such as *graphics processing units* (GPUs) and *digital-signal processors* (DSPs) where the problem domain is well defined and the markets large enough to support their production. In particular, GPUs have developed to support greater levels of programmability, and consequently have found applications in other areas that fit their restricted model of parallelism. In these cases, GPUs can provide significant improvements in performance, but they remain used typically as an accelerator in conjunction with a conventional SMP to handle sequential execution and more general forms of parallelism. This *heterogeneous* approach is at odds with a single basic model of computation since it essentially argues for a variety of special-purpose designs.

#### 1.2. General-purpose parallel computers

Parallelism has been deployed in specific domains with great success but a more general model has not yet emerged. For parallelism to succeed sequential computing and become the *standard form*, a model analogous to the von Neumann general-purpose sequential computer is required that embodies the same concept of efficient universality [Val88, McC93]. Such a model would enable standardisation between architectures and high-volume production, leading to optimised manufacturing processes and low-cost devices, and the development of software that could not only be used on different parallel machines, but also on successive generations in order to benefit from new technologies to deliver increasing levels of performance [May94]. The emergence of large consumer-based markets, for instance robotics, could drive this.

Surprisingly, Valiant has already described the essential aspects of a basic model of parallel computation [Val90b] and it is based on parallel communication networks that can support arbitrary patterns of communication. These provide *architectural independence* by allowing a separation of the implementation of a program from the structure of a machine implementation, with both conforming to the basic computational model. Crucially, architectural independence simplifies the process of writing and compiling *efficient* programs because the machine structure does not need to be taken into account.

In the analogy with the von Neumann model, structural independence corresponds to the abstraction of the memory that supports arbitrary patterns of access but this depends on memory implementations having to invest heavily in the structure and interconnection to deliver this capability. In the 1950s, before the advent of magnetic storage technology that could deliver random access efficiently, *ultrasonic memories* such as *mercury delay lines* had non-uniform behaviour and a great deal of effort was invested to optimising accesses with *optimum codings* to reduce delay [Wil68]. This however significantly complicated the programming of systems with these memories and tied programs to specific memory implementations. Random-access memory facilitated a simple programming model for sequential processors and, up until the mid-1980s, memory latency corresponded closely to computational operations such as arithmetic and branching. In the C programming language [KR88] up to this time, each primitive operation corresponded to one machine operation (memory access or otherwise), providing the programmer with a simple performance model and efficient and predictable execution [Myc07]. However, as the performance of memory has deteriorated with respect to processor speeds, architectural optimisations such as caches have led to the need for programming and compilation approaches that can leverage these and consequently, C has lost its close correspondence to sequential machines and its utility as a simple abstraction.

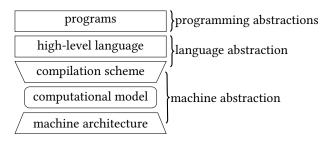

The essential aspects of a *practical* general-purpose model of computation are therefore a universal machine that can be implemented efficiently with current technology, a high-level language that can express arbitrary programs and a compilation process that can transform programs written in the language to execute efficiently on the machine. In this, there are three key *abstractions*; first, the universal nature of the machine provides an *abstraction of its implementation*, second, the high-level programming language provides a further *abstraction of the machine* to provide the programmer with primitive constructs that are convenient to use to express computational structures, and third, the language also provides the ability to create *new abstractions* such as subroutines, modules and libraries, to simplify the expression of complex program structures.

Figure 1.1 below summarises the components of general-purpose computation and abstractions involved.

**Figure 1.1.:** Components of a general-purpose form of computation and the abstractions involved. The shape of the compilation-scheme component is tapered to represent a *reduction* from the high-level language to the computational model and the machine-architecture component is also tapered to reflect that the computational model captures only the essential features of the implementation.

#### 1.3. This thesis

This thesis practically demonstrates the essential aspects of a general-purpose model of parallel computation by proposing a scalable *Universal Parallel Architecture* (UPA) based on a fast, highly-connected communication network and a high-level programming language called sire that corresponds closely to the UPA because it can be compiled using simple techniques. It evaluates both the implementation cost of the UPA using current technologies and its performance, focusing on specific sire programs as well as its ability to support sequential programming techniques.

# 1.3.1. Contributions

## The UPA design

- 1. An architecture that can support the efficient execution of highly-parallel programming techniques as well as sequential ones, and that can switch between these during the execution of a program.

- 2. An architecture that allows implementations of it to be easily specialised by adjusting the network performance or balance of processing to memory to optimise for specific workloads.

- 3. The choice of a folded-Clos network for the interconnect topology, based on:

- a) its equivalence to the hypercube and fixed-degree variants and consequent universality as a communication network, and its ability to support two-phase randomised routing with no increase in the average distance that messages travel;

- b) its hierarchically recursive structure that allows it to be packaged with different technologies and for bandwidth to be flexibly provisioned at each level.

- 4. The use of a high-degree crossbar switching element to reduce the number of stages in the folded-Clos network and to connect multiple processors to each switch.

- 5. The use of wormhole switching and a remote memory access mechanism to efficiently support both arbitrary-sized messages and memory accesses.

- 6. The use of XMOS XS1 processor cores that provide direct support for communication and parallelism to minimise *communication startup latency* and the cost of creating parallel processes respectively, so that the degree of parallelism exploited from a particular problem can be maximised.

# The sire programming language design

- 7. The ability to express and combine a wide range of *programming paradigms*, including messagepassing and data-flow structures, task farms and event handlers, in particular, PRAM-style shared-memory parallel computations and RAM-style sequential computations.

- 8. The concept of a *server* as a language primitive:

- a) to provide a mechanism for *sharing* within a message-passing framework (i.e. combining the capabilities of shared memory programming with those of message passing), where sharing in this context relates to many-to-one patterns of communication;

- b) to provide a basis for distributed parallel subroutines, distributed representations of data (as a basis for distributed data structures) and the modular composition of a program;

- c) to deal with all aspects of abstraction that involve communication, allowing processes to be named (rather than having named communication channels as was the case in occam) in order to facilitate a simple distributed implementation;

- d) to provide a mechanism for explicitly moving pieces of program to the data on which they operate (i.e. between processors);

- e) with declaration syntax similar to standard variable declarations so that a program can be composed in a conventional way with a sequence of declarations followed by a a sequence of operations;

- f) with call syntax similar to local procedure calls to allow a programmer to move easily between local and remote forms of a call to employ parallelism or to distribute data.

- 9. Facilities for combining collections of servers and creating abstractions based on them.

- 10. The capability of sire to be compiled using simple techniques (i.e. with a non-optimising compiler) and therefore for the primitive aspects of the language to correspond closely to the operation of the UPA, providing a *transparent execution model*.

11. For sire to be used as a 'system' programming language because of its close correspondence to the UPA. This, for example, allows it to be used to build components for managing and optimising distributed systems such as memories with a particular model of consistency, caches to transparently improve locality and facilities for replication and combining to manage distributed data.

#### Compilation of sire programs to the UPA

- 12. For a large part of the sire compilation process to be dealt with using source-to-source program transformations into to a simplified *canonical form*, using algebraic properties of the language. This is beneficial because the output is understandable by the programmer and only the small canonical subset needs to be implemented.

- 13. A compile-time scheme to determine a run-time schedule for the allocation of processes to processors. This avoids the overheads of run-time processor allocation and thus minimises the overhead of using distributed parallelism.

- 14. Efficient run-time distribution of program code between the memories of different processors to reuse processor memory. This also decouples the compilation process and its run time from the number of processors in the target system and allows minimal program binaries to be produced (i.e. not one for each processor) that can be replicated rapidly over a system at boot time.

- 15. A compile-time scheme to prevent deadlock that can be caused by many-to-one server channel connections. This is based on queuing of client requests by servers to engage with them, so that client requests do not block other communication traffic in the network.

#### Performance evaluation of the UPA and sire

- 16. A high-level implementation model of the UPA, based on a packaging of a folded Clos using a H-tree layout and a simplified VLSI model with specific parameters to characterise current technology.

- 17. Evaluation of the cost and scaling of the UPA implementation, demonstrating that the overall investment in a universal interconnect for a system with up to 4,096 processors is around 20% to 30% of the total cost, compared to 5% with a non-universal 2D mesh network.

- 18. Evaluation of the performance of the primitive mechanisms for parallelism, communication and abstraction in sire, demonstrating that the overheads are very low:

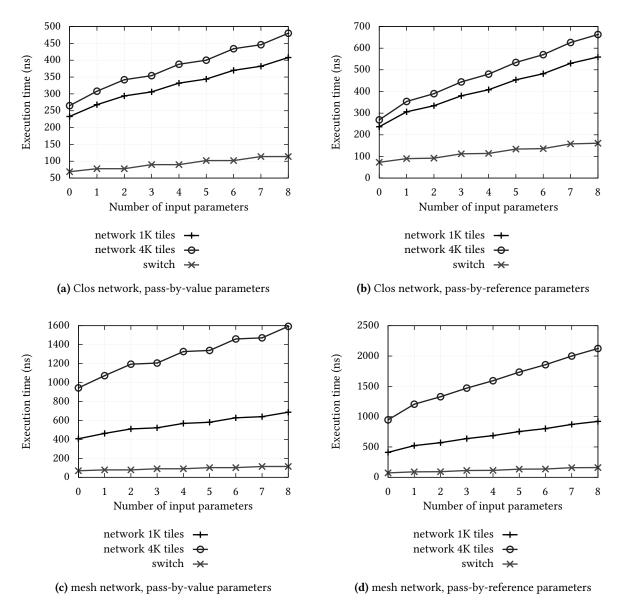

- a) remote server calls, performed across the network, have an overhead of 8 to 20 times that of local calls;

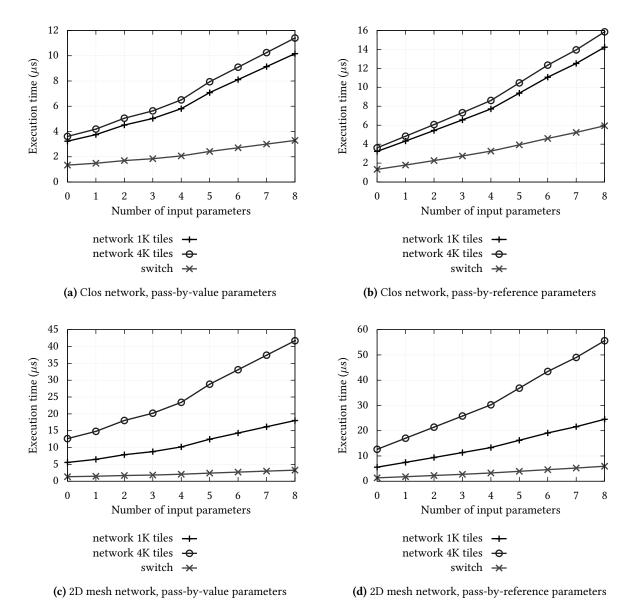

- b) processes can be offloaded to remote processors if they exceed just a few tens of thousands of operations (around 10  $\mu$ s to 60  $\mu$ s at 1 GHz);

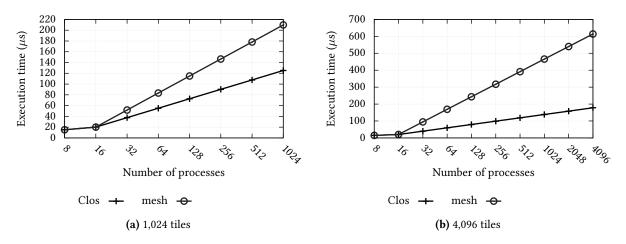

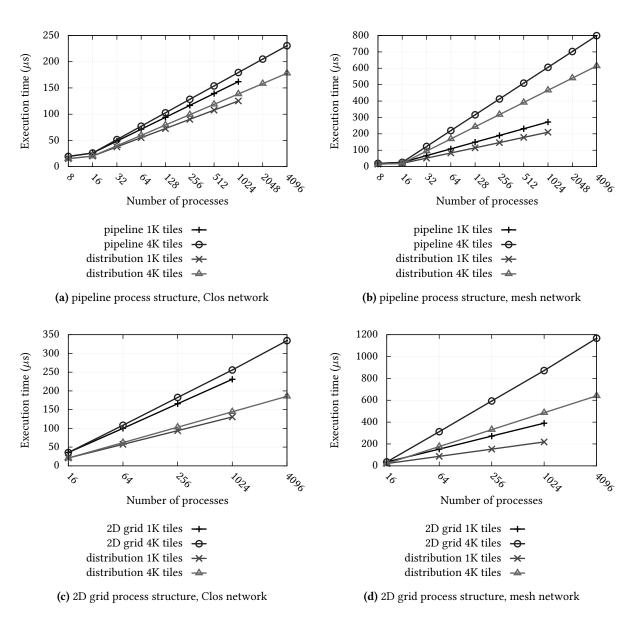

- c) the mechanism for process distribution can bring thousands of processors into action in a few thousand cycles (4,096 tiles in around 200  $\mu$ s at 1 GHz).

- 19. A compiler for a simple sequential language that generates programs to execute on the UPA with a large emulated memory.

- 20. Evaluation of the ability of the UPA to support sequential programming techniques by emulating large random access memories. The results of this show that general sequential programs can be emulated with a factor of 2 to 3 slowdown when compared to conventional sequential architectures.

#### 1.3.2. Overview

This thesis is divided into three parts: background, the description of the UPA and sire, and performance evaluation. Each chapter deals with different components of the 'stack' in Figure 1.1 and with each summary below, an illustration of the components it corresponds to is included.

The background part consists of three chapters.

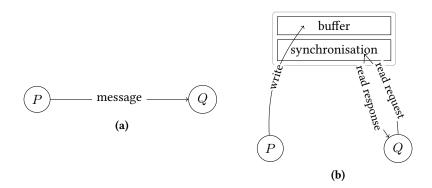

- Chapter 2 considers the concept of parallel computation independently of any particular architecture or programming language. It focuses on the two main communication paradigms: *shared memory* and *message passing* and argues why conventional shared memory is insufficient for a general model of parallelism.

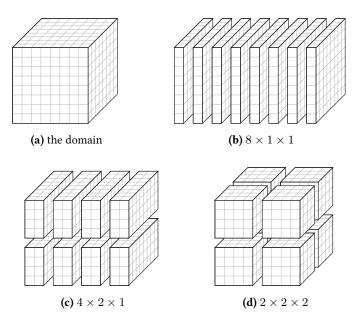

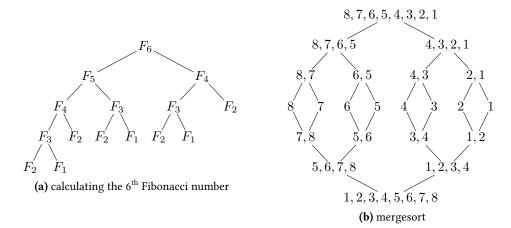

- Chapter 3 discusses parallel programming, from high-level issues related to the formulation of an algorithm, to the issues that affect the effectiveness with which a particular language can be compiled. It outlines criteria for a general-purpose parallel language and presents a survey of existing programming approaches.

- Chapter 4 describes the theoretical results concerning universal networks, describes the practical details of an implementation of an interconnection network and presents a short survey of existing parallel machines.

The UPA and sire language part consists of four chapters.

- Chapter 5 presents a description of the UPA and an explanation of its main characteristics.

- Chapter 6 presents a definition of the sire programming language that introduces it incrementally and, for each part, provides simple examples of its use.

- Chapter 7 demonstrates a range of high-level programming *structures* that can be expressed with sire and how they can be combined to form complex programs. The chapter is divided into message-passing *process structures* and *server structures*.

| $\square$ | machine     |   |

|-----------|-------------|---|

|           | model       | ) |

|           | compilation |   |

|           | language    |   |

|           | program     |   |

| programs  |             |   |

|-----------|-------------|---|

| sire      |             |   |

|           | compilation |   |

| (         | model       | ) |

| $\square$ | UPA         |   |

7

Chapter 8 describes how sire programs can be compiled. It is divided into a description of the sequence of *transformations* applied to convert a program into canonical form, and a description of the generation of executable code and its combination with run-time program components.

The evaluation of implementation cost and performance part consists of two chapters.

- Chapter 9 describes a *realistic* implementation model for the UPA, based on current production technologies, and presents a range of hypothetical systems to show how the relative proportions of processing, interconnect and memory scale.

- Chapter 10 presents the methodology and results for the empirical performance investigations based on the modelled implementation of the UPA from Chapter 9. The first set of experiments investigate the efficiency of the primitive mechanisms for parallelism and communication in sire and the second set of experiments investigate the ability of the UPA to support sequential programming techniques.

Finally, Chapter 11 provides a summary and conclusion.

|                  | sire        |   |  |

|------------------|-------------|---|--|

|                  | compilation |   |  |

| $\left( \right)$ | model       | ) |  |

| $\square$        | UPA         |   |  |

|           | programs    |   |

|-----------|-------------|---|

|           | sire        |   |

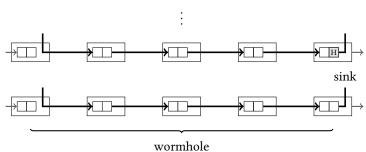

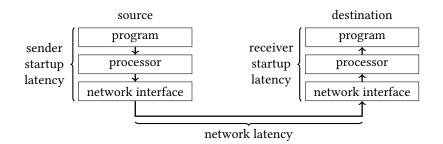

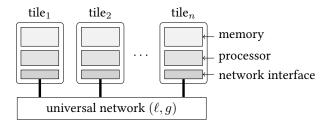

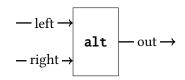

|           | compilation | ] |